摘要:首先介绍异步FIFO的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法;在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA实现。 关键词:异步电路 FIFO 亚稳态 格雷码 ...

”EDA/PLD中的异步FIFO结构及FPGA设计 EDA/PLD“ 的搜索结果

本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。这种异步FIFO比外部FIFO 芯片更能提高系统的稳定性。 1 FIFO的基本结构和工作原理 FIFO(First In First Out)是一种采用环形...

FPGA内部具有丰富的存储单元,易于实现各种存储器(如FIFO、双口RAM等);另外,基于查找表的逻辑单元可用于实现各种数字信号处理(如滤波等),以辅助DSP处理器做各种预处理。 TI公司推出的高性能数字信号处理芯片...

目前,复用器的设计方案主要基于DSP(数字信号处理器)的实现技术,这种设计方法在理论上也能实现对传送流的复用,考虑到实现复用器诸多高速、复杂的逻辑功能,同时,FPGA(现场可编程门阵列)理论上可以无限次地重新...

为了解决嵌入式实时数据采集系统中,高速采集数据量大,而处理器的处理速度有限的矛盾,保证数据不丢失并提高处理器的数据吞吐率,文中提出一种基于FPGA(现场可编程门阵列) 实现的最优FIFO(先入先出存储器) 结构设计...

UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器)是广泛使用的...或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个

UART(Universal Asynchronous Receiver/Transmitter,通用异步收发器)是用于控制CPU与串行设备通信的芯片,将由CPU传送过来的并行数据转换为输出的串行数据流。将系统外部来的串行数据转换为字节,供系统内部使用...

根据UART接口特点和应用需求,以提高VHDL设计的稳定性和降低功耗为目标,本文讨论了UART接口中时钟域划分、时钟分频、亚稳态、同步FIFO设计等问题和解决方案。 关键词:通用异步串行接口 VHDL 亚稳态 现场可编程...

通过集成FPGA逻辑与嵌入式电路,PolarPro器件的电路实现了高速总线对总线接口、双端口SRAM模块以及共位异步FIFO控制器、高费效比DDR存贮器扩展以及时钟管理单元。PolarPro器件的所有电路均能用新的超低功耗模式(VLP)...

摘要:本文提出了基于FPGA正码速调整的设计方案,采用格雷码对地址编码的异步FIFO设计,并利用MAXPLUSⅡ进行编译和仿真。结果表明,设计方法切实可行。 1 引言 在时分制数字通信系统中,为了扩大传输容量和...

l 引 言UART(Universal Asynchronous Receiver/Transmitter,通用异步收发器)是用于控制CPU与串行设备通信的芯片,将由CPU传送过来的并行数据转换为输出的串行数据流。将系统外部来的串行数据转换为字节,供系统内部...

摘要:激光雷达的发射波及回波信号...介绍了ADC外围电路、工作时序以及DSP的EMIF的设置参数,并对异步FIFO数据读写进行仿真,结合硬件结构详细地分析设计应注意的问题。系统采样率为30 MHz,采样精度为12位。 0 引言

摘要:主要讨论了FPGA在多单片机串行读数系统中的应用,在该系统中单片机通过异步串行通信读取外部设备中的数据,经FPGA缓冲后再送到USB单片机,最终上传到计算机。文中重点介绍了利用FPGA内部双口RAM构建的FIFO在该...

数字电路(fpga/asic)设计就是逻辑电路的实现,这样子说太窄了,因为asic还有不少是模拟的,呵呵。我们这里只讨论数字电路设计。实际上就是如何把我们从课堂上学到的逻辑电路使用原理图(很少有人用这个拉),或者硬件...

System-on-Progammable-Chip -- SoC 片上系统 Application Specific Integrated Circuit -- ...PL FPGA 可编程逻辑 Intellectual Property -- IP 知识产权 Register Transfer Level -- RTL 寄存器传输级 On-Chip M...

1、简述建立时间和保持时间 建立时间Tsu(setup):触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。 保持时间Th(hold):触发器在时钟上升沿到来之后,其数据输入端的数据必须保持...

这些知识点确实都很实用,这些设计思想或者也可以说是经验吧,是很值得每一个有志于FPGA/CPLD方面发展的工程师学习的。 1、硬件设计基本原则 (1)、速度与面积平衡和互换原则:一个设计如果时序余量较大,...

校园招聘即将开始,是时候回顾一下FPGA设计基础,顺便记录一下求职期间的一些经历。 线与逻辑 线与逻辑:即两个输出端(包括两个以上)直接互连就可以实现"AND"的逻辑功能。在总线传输等实际应用中需要多个门的输出端...

C、异步FIFO不能用于解决亚稳态问题 D、对于多比特数据可以采用握手的方式来消除亚稳态 *2,关于FPGA芯片内存储器资源描述错误的是(C)。 A、FPGA内部有BLOCK RAM存储器 B、BLOCK RAM由一定数量固定大小的存储块...

FPGA 的结构是查找表结构,其程序不用去太考虑芯片的结构,要注意的是时序上问题,它的结构比较复杂,功能也很强大,一般应用在通信领域等比较高端的场合,FPGA 是用来设计芯片的芯片。硬件以强大的并行方式来响应...

1 、wire型和reg型 wire网线型表示硬件单元之间的连线,值由驱动单元决定,...连续赋值常以assign为关键词,用"="赋值,赋值的对象是wire型用于驱动wire网线,assign不能出现在always和initial语句中。 示例:assig...

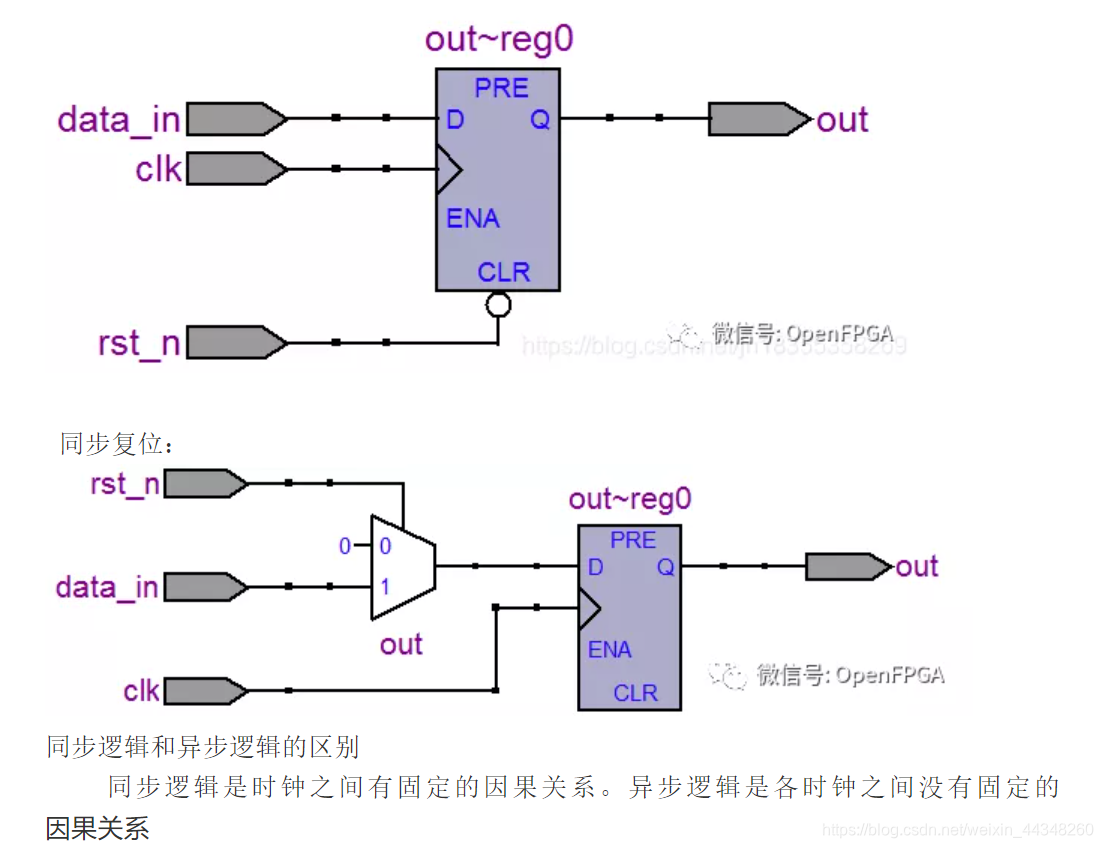

...1:什么是同步逻辑和异步逻辑? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时...

文章目录FPGA 的发展历史FPGA是什么FPGA的应用场景FPGA 相较于"其他可替代产品"的优势FPGA组成 FPGA 的发展历史 小型的 通用数字集成电路 我们从逻辑功能的特点上将数字集成电路分类,可以分为通用型和专用型两类。...

数字逻辑与EDA技术期末考试复习重点

面试——FPGA常见问题1

标签: 面试

首先阐释为什么在 PLD 设计中要采用同步时序设计,然后重点论述同步时序设计的要点。 本文内容为阅读一些书籍的摘录内容,仅供参考。 一、异步时序设计与同步时序设计 简单比较 异步电路和同步电路的异同。 1.异步...

推荐文章

- Python菜鸟晋级04----raw_input() 与 input()的区别_pycharm没有raw input-程序员宅基地

- 高通AR增强现实多卡识别和扩展跟踪Unity_imagetarget扩展追踪-程序员宅基地

- 对于三星手机的手工root方法-程序员宅基地

- 2021年佛山高考成绩查询,2021年高三佛山一模,看佛山高中排名-程序员宅基地

- 删除并清空应收应付模块 期初数据_应付管理系统怎么清除数据-程序员宅基地

- 嵌入式固件加密的几种方式-程序员宅基地

- 非root情况下访问手机存储位置权限的方法_不root 通讯录 存放目录-程序员宅基地

- Mybatis项目开发流程_使用mybatis的开发步骤-程序员宅基地

- 三方协议,档案,工龄,保险,户口,-程序员宅基地

- 华为交换机命令 端口速率_华为S5700交换机的端口QOS限速问题-程序员宅基地